| l. Publicação nº                                                                    | 2. Versão                                                                              | 3. Data                                                                                | 5. Distribuição  Interna 🖾 Externa                                                                                                                                                                               |

|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INPE-3224-PRE/575                                                                   |                                                                                        | Agosto, 198                                                                            | -                                                                                                                                                                                                                |

| 4. Origem                                                                           | rograma                                                                                |                                                                                        | Restrita                                                                                                                                                                                                         |

| DCA/DEA                                                                             | SUBORD                                                                                 | 2-1-1 sutants                                                                          | )                                                                                                                                                                                                                |

| DCA/DEA  6. Palavras chaves - S  MICROPROGRAMAÇÃO -  SIMULAÇÃO  SISTEMA DE DESENVOL | TESTES                                                                                 |                                                                                        | :5 /                                                                                                                                                                                                             |

| 7. C.D.U.: 681.326.32                                                               |                                                                                        |                                                                                        |                                                                                                                                                                                                                  |

| 8. Titulo INPE-3224-PRE/575                                                         |                                                                                        |                                                                                        | <sup>5</sup> 10. Pāginas: 06                                                                                                                                                                                     |

| "S-MICRO - SISTEMA PARA SIMULAÇÃO DE UNIDADE<br>DE CONTROLE MICROPROGRAMADA"        |                                                                                        |                                                                                        | 11. Ültima pägina: 05                                                                                                                                                                                            |

| <i>p</i> B 000.22.00                                                                |                                                                                        |                                                                                        | 12. Revisada por                                                                                                                                                                                                 |

| 9. Autoria Ronaldo Luiz Dias Cereda<br>José Carlos Maldonado                        |                                                                                        |                                                                                        | p/ Risenda J. Marcos A.C. Cruz                                                                                                                                                                                   |

| Assinatura responsáve                                                               | D                                                                                      |                                                                                        | 13. Autorizada por acado Nelson de Jesus Parada Diretor Geral                                                                                                                                                    |

| 14. Resumo/Notas                                                                    |                                                                                        |                                                                                        |                                                                                                                                                                                                                  |

| tais microprogramad<br>gral da unidade de<br>tar o desenvolvimen                    | os, cujo objet<br>controle micro<br>to integrado o<br>proprio sister<br>es, tanto do l | oprogramada. E<br>da arquiteturo<br>ma microprogra<br>ponto de vista<br>ens sobre outi | olvimento de sistemas digi<br>e permitir a simulação inte<br>Procura-se com isso facil<br>a da unidade de controle, d<br>mado em teste. Apresenta-s<br>a de "hardware" quanto d<br>ras proposições, destacando-s |

| 15. Observações<br>Trabalho aprese<br>19 Congresso Lo                               | , la ma 50 C                                                                           | en rugago Bras                                                                         | ileiro de Automâtica/                                                                                                                                                                                            |

Ronaldo Luiz Dias Cereda José Carlos Maldonado

Conselho Nacional de Desenvolvimento Científico e Tecnológico - CNPq Instituto de Pesquisas Espaciais - INPE Departamento de Engenharia de Computação em Aplicações Espaciais - DCA Caixa Postal 515 - São José dos Campos - SP - Brasil

#### Resumo

Propõe-se um sistema para desenvolvimento de sistemas dígitais micropro gramados, cujo objetivo principal é permitir a simulação integral da unidade de controle microprogramada. Procura-se com isso facilitar o desenvolvimento integrado da arquitetura da unidade de controle, do microprograma e do próprio sistema microprogramado em teste. Apresenta-se o sistema em detalhes, tanto do ponto de vista de "hardware" quanto de "software", bem como suas vantagens sobre outras proposições já existentes, destacando-se suas diferenças e algumas limitações.

#### Abstract

A system for development of microprogrammed digital systems is proposed, whose main design goal is to permit the whole simulation of the microprogrammed control unit. This way an effort is made to facilitate the integrated development of the control unit architecture, of the microprogram and even of the microprogrammed system under test. The system is introduced in detail both from the hardware and the software point of view. Its advantages over other existing propositions are also introduced, emphasizing its differences and a number of limitations.

### 1. INTRODUÇÃO

A técnica de microprogramação está sendo largamente aplicada no desenvolvimento de di versos equipamentos, nas mais diferentes áre as de aplicação de sistemas digitais. Algumas vantagens da implementação de circuitos de controle microprogramados em relação à implementação que utiliza logica aleatoria podem ser citadas (Amaral, 1979):

- 1 Arquitetura melhor estruturada que resulta em uma redução da lógica aleatória na unidade de controle do sistema.

- 2 A emulação de vários dispositivos (não somente processadores) pode ser feita por um unico dispositivo de proposito geral alteran do o conteúdo de sua memoria de controle.

- 3 Rotinas de diagnose e manutenção podem ser fácil e eficientemente implementadas na unidade de controle do sistema.

- 4 Mudanças e adaptações específicas que se façam necessárias no sistema podem, em prin cípio, ser facilmente realizadas alterando o conteúdo da memória de controle.

- 5 O desempenho de dispositivos microprogra mados pode ser aumentado com custos menores que os custos para sistemas de lógica aleató ria.

6 - Documentação e custos de treinamento de manutenção podem ser reduzidos.

Pode-se perceber que as vantagens dos sis temas microprogramados sobre os enfoques con vencionais dependem dos recursos disponíveis para desenvolvimento, teste e manutenção des tes sistemas.

Os recursos para desenvolvimento de sis temas microprogramados disponíveis atualmen te no DCA/INPE compreendem basicamente:

- 1 Emulador de Memórias de Microcontrole Au xiliado por Computador (EMMAC): este sistema permite ao usuário depurar um microprograma durante a fase de teste e facilita a diagno se e manutenção do protótipo final (Amaral, 1979).

- 2 Linguagem de Microprogramação (LMP): é uma linguagem para geração de microcódigos (Yamaguti, 1981).

Estes recursos formam o sistema LMP/ EMMAC, que constitui um sistema completo pa ra geração e depuração de microprogramas.

No entanto o LMP/EMMAC é uma ferramenta de desenvolvimento - no que tange a micropro gramas - restrita ao âmbito da memoria de con trole. Para sua utilização é necessário que toda a lógica de sequenciamento tenha sido implementada, pelo menos como protótipo. Es ta característica torna mais difícil realizar as alterações necessárias na lógica de se quenciamento decorrentes da aplicação dos microprogramas no sistema microprogramado.

Neste sentido, o S-MICRO é um sistema de desenvolvimento para sistemas microprograma dos, configurado parte em"hardware" e parte em "software", o qual propicia a simulação in tegral da Unidade de Controle Microprograma da, ou seja, o sequenciador, a memoria de controle, a logica de decodificação e mapea mento etc. Esta característica o coloca vantagem sobre outras proposições por facili tar, em muito, redefinições e/ou alterações decorrentes da observação dos compromissos entre o microprograma e o sistema micropr<u>o</u> gramado durante a fase de especificação do Bistema.

Outra vantagem desta proposição é a via bilidade de implementação, através do S-MI CRO, de facilidades na execução dos testes dos microprogramas tais como: execução pas so-a-passo, "breakpoints", etc que serão des critas na Seção 3.2.

### 2. ARQUITETURA DO S-MICRO

A ideia basica que norteou a especifica ção da arquitetura do S-MICRO é a de facilitar a interação do usuário com os recursos para desenvolvimento de sistemas microprogramados, bem como com o proprio sistema em teste. A ligação com um computador de grande porte (B-6800), no qual está residente o tradutor LMP, acrescenta facilidades na geração de microprogramas, alem de permitir a utilização dos recursos de entrada e saída e de armazenamento de dados deste computador.

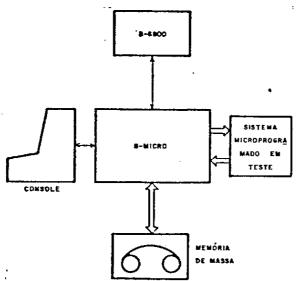

Uma visão geral do ambiente de utiliza cão do S-MICRO pode ser encontrada na Figura 2.1.

Fig. 2.1 - Ambiente de utilização do S-MICRO.

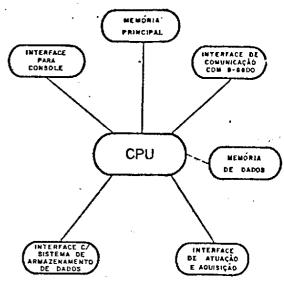

Do ponto de vista de "hardware", o S-MI CRO é composto de sete unidades funcionais, conforme a Figura 2.2. O "software" do siste ma, denominado "Software de Simulação" sera descrito na Seção 3.

Fig. 2.2 -Unidades funcionais do S-MICRO.

O microcomputador de propósito geral AS TRO-L/V1. desenvolvido no DCA/INPE, prove as características funcionais adequadas para a configuração do S-MICRO, a menos da Interface de Atuação e Aquisição - que permite o interfaceamento com o sistema microprogramado - e da Memória de Dados, a serem descritos nas se ções seguintes.

No ASTRO-L/VI a unidade CPU e implementada com o processador de 16 bits TMS 9900 (Texas Instruments), com capacidade de endere camento de memoria de 64K "bytes" (32K pala vras).

## 2.1 - CARACTERÍSTICAS DA INTERFACE DE ATUZ CÃO/AQUISIÇÃO (IAA)

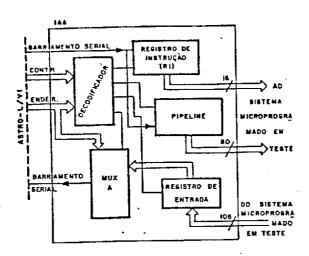

Esta interface prove facilidades de "hardware" para atuação/aquisição nos circui tos digitais que compõem o sistema microprogramado. O diagrama de blocos da IAA é forne cido na Figura 2.3.

Os registros RI. PIPELINE e de ENTRADA podem ser carregados ou lidos através do barramento serial do ASTRO-L/VI. As entradas é saídas desta interface são conectadas aos circuitos do sistema microprogramado em teste, através de garras individuais que permitem uma maior flexibilidade na atuação/aquisição.

### 2.2 - ALOCAÇÃO DA MEMÓRIA DE CONTROLE

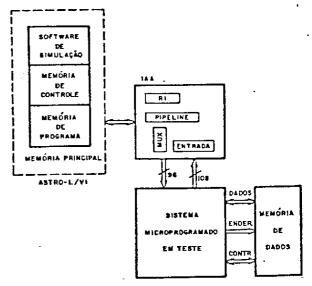

A memoria de controle, onde está alocado o microprograma a ser depurado, é simulada utilizando parte da Memoria Principal do ASTRO-L/VI, conforme a Figura 2.4. Esta filoso fía acrescenta maior flexibilidade ao siste ma, em aspectos como: o tamanho da Memoria de

Fig. 2.3 - Diagrama de blocos da IAA.

Controle poderá ser definido pelo usuário; o comprimento da palavra de controle esta rá limitado apenas pelo "hardware" da IAA, já que sepodem utilizar posições consecuti vas da Memoria Principal do ASTRO-L/V1 para armazenar uma única microinstrução; e altera ções do conteúdo da Memoria de Controle pode rão ser realizadas com maior facilidade.

Além destas facilidades, este enfoque possibilita maior aproveitamento da ligação existente com o B-6800, pois habilita o car regamento dos microcódigos gerados através do tradutor LMP residente naquele computador diretamente na Memória de Controle simulada.

A transferência das microinstruções da Memória de Controle para o registro PIPELINE é feita através do "Software de Simulação". Em cada vez são transferidas N palavras de posições contíguas da Memória Principal, que definem uma microinstrução, para o registro PIPELINE, onde N<>5. A microinstrução corrente fica estável neste registro enquanto executa as microoperações sobre os recursos de "hardware" do sistema microprogramado em teste; desta forma o registro assume funções idênticas aos tradicionais registros "pipeline" utilizados em projetos microprogramados.

## 2.3 - ALOCAÇÃO DAS MACROINSTRUÇÕES

As macroinstruções, que constituem o programa a ser executado pelo sistema microprogramado em teste, e que são interpretadas pelo microprograma e, consequentemente, executadas pelo "hardware" deste sistema, estão alocadas num trecho da Memória Principal do ASTRO-L/V1, denominado "Memória de Programa", conforme ilustrado na Figura 2:4.

Estas macroinstruções são transferidas pelo "Software de Simulação", sob o contro le do microprograma, para o Registro de Instrução (RI). Este registro, localizado na IAA, tem 16 bits cujas saídas são ligadas direta mente ao "hardware" do sistema em teste.

É importante notar que todo o processo de

"fetch" da macroinstrução não é realizado em nível de microprograma, como seria usual nu ma maquina microprogramada. Isto se deve ao fato de que o registro RI, que normalmente integra o "hardware" da maquina microprogramada, está implementado na Interface de Aquisição/Atuação (IAA). Para que o processo de busca da próxima macroinstrução seja pos sível, é necessário que o "Software de Simulação" tenha acesso às informações de contex to do sistema microprogramado, como por exem plo: PC, registros de uso geral etc, através do REGISTRO DE ENTRADA da IAA.

· Fig. 2.4 - Alocação de memória no S-MICRO

Esta solução implica que toda a lógica de decodificação e mapeamento seja implemen tada também pelo "Software de Simulação", o que acrescenta uma flexibilidade ainda maior à depuração do microprograma e do proprio programa do sistema em teste.

Uma possível restrição de memoria para armazenamento de programa não deve ser enca rada como uma limitação do S-MICRO, pois o seu objetivo é fornecer subsídios para especificação de unidades de controle micropro gramadas e de seus microprogramas, e não para desenvolvimento de programas a serem executados no sistema microprogramado. Portanto a área de "Memoria" de Programa "necessária é, em princípio, igual à cardinalidade do conjunto de macroinstruções da maquina microprogramada.

# 2.3.1 - AREA DOS DADOS ASSOCIADOS ÀS MACRO INSTRUÇÕES

Na hipostese de haver dados associados à execução das macroinstruções, eles 'estarão alocados na unidade denominada "Memoria de Dados", conforme pode ser visto na Figura 2.4

O acesso a esta unidade é realizado, de maneira convencional pelo "hardware" do proprio sistema microprogramado, ou seja, atra vés de linhas de Dados, Endereços e Contro le. Esta divisão da Memoria Principal do sis

tema microprogramado em "Memória de Dados" e "Memória de Programa" evidentemente só tem significado durante a fase de simulação da unidade de controle.

A não-existência da "Memoria de Dados" acarretaria uma complexidade indesejavel no "software" do S-MICRO: o "Software de Simila ção", responsável pelo mapeamento e pelo sequenciamento das microinstruções, teria também de realizar a simulação das microins truções de acesso à Memoria Principal, o que seria altamente indesejável, pois desta for ma as microinstruções deste tipo, que 880 parte bastante significativa do microprogra ma, não poderíam ser testadas e validadas, bem como os recursos de "hardware" associa dos.

## 2.4 - MANIPULAÇÃO DE BITS DE CONDIÇÃO E DE STATUS

O "Software de Si. lação" realiza princi palmente as funções de sequenciamento do mi croprograma. Estas funções exigem, em cer tos momentos, testes de informações de status e de "bits de condição" da maquina micro programada para que decisões sejam tomadas adequadamente. Estas informações podem ser lidas pelo "Software de Simulação" atravês do REGISTRO DE ENTRADA da IAA.

Desta forma o Mux A da Figura 2.3 realiza, nestes momentos, funções semelhantes as dos "Mux de Condições" ("Conditional Mux") tradicionais em unidades de controle micro programadas.

Como dito anteriormente outras informa ções são adquiridas através destes recursos (REGISTRO DE ENTRADA e Mux A), tais como PC, registros de uso geral etc., provenientes do sistema em teste.

## 3 - "SOFTWARE DE SIMULAÇÃO"DO S-MICRO (SS)

O S-MICRO é composto, do ponto de vista de "software", conforme ja dito anteriormen te, de um "Software de Simulação" (SS) cujas funções básicas são: aquisição, decodificação e mapeamento das macroinstruções, e sequen ciamento das microinstruções.

Além destas funções básicas, o SS provê recursos de interação com o usuário através do console do sistema, bem como facilidades para a depuração de microprogramas e do proprio sistema microprogramado através da implementação de modos de operação, os quais serão descritos posteriormente. Além destas facilidades, foram especificados recursos de depuração também em nível do conjunto de macroinstruções.

O SS está alocado na Memória Principal do ASTRO-L/V1, conforme Figura 2.4, e interage diretamente com a IAA.

O SS é implementado com o apoio de uma linguagem de alto nível ALGOL-M (Martins, 1976), cujo compilador reside no computador B-6800. A utilização de uma linguagem com es tas características favorece o desenvolvimen to estruturado e modular do SS. Este contex to torna altamente flexível o projeto da lo

gica de sequenciamento da unidade de contro le, que é simulada pelo SS, pois redefinições e alterações necessárias nesta lógica, resultantes dos procedimentos necessários nesta lógica, resultantes dos procedimentos de teste, são facilmente realizaveis.

Esta característica torna o S-MICRO sistema de desenvolvimento e depuração de sis temas microprogramados diferente dos sistemas propostos de desenvolvimento convencionais até então. No entanto surge uma restrição de corrente deste enfoque, ou seja, a taxa carregamento das microinstruções no registro de "pipeline" não é constante e, na maioria das vezes, não atende as necessidades de ve locidade dos sistemas microprogramados em tes te, o que impede a sua validação em tempo real. Deve-se ressaltar também que a flexibi lidade conseguida através deste enfoque in corre na perda de paralelismo de microopera ções obtido com a implementação em"hardware" do sequenciador.

## 3.1 - DESCRIÇÃO DOS MÓDULOS FUNCIONAIS BÁSI COS DO SS

O SS compõe-se basicamente dos seguintes modulos funcionais:

- 1 Aquisição de Macroinstrução: realiza o "fetch" da macroinstrução com base nas infor mações lidas no REGISTRO DE ENTRADA e carre ga-a no registro RI da IAA. A área de dados manipulada por este módulo é fundamentalmen te a Memoría de Programa (Figura 2.4).

- 2 Decodificação e Mapeamento: realiza a de codificação do "opcode" da macroinstrução e utiliza o resultado desta decodificação para acessar o endereço de ínicio do microprogra ma que interpreta esta macroinstrução. A es trutura de dados associada a este modulo e uma tabela que contém os endereços citados acima.

- 3 Sequenciamento de Microinstruções: realiza repetitivamente a carga do registro PIPE LINE com a microinstrução corrente, alem de decodificar o tipo de microinstrução e bus car a próxima microinstrução. As áreas de da dos associadas a este modulo são a Memória de Controle e os parâmetros lidos através do REGISTRO DE ENTRADA da IAA.

## 3.2 - FACILIDADES DE DEPURAÇÃO OFERECIDAS PE LO SS.

Em todas as etapas envolvidas no proces so de desenvolvimento e depuração de siste mas microprogramados, o S-MICRO oferece facilidades de monitoração através de amostragem de resultados e informações na tela do conso le. Estes resultados e informações podem ser especificados pelo úsuário, bem como o proprio formato (modos de leitura) em que eles deverão ser fornecidos.

Visando fornecer maior potencial de depuração, foram definidos "Modos de Operação" selecionáveis pelo usuário. Estes "modos" diferem quanto a quantidade de microinstruções a serem executadas cada vez. Existem três modos, descritos a seguir:

- 1 "Por microinstrução": Após a carga de uma microinstrução no registro PIPELINE, o operador poderá requerer a amostragem de resultados a partir dos modos de leitura oferecidos.

- 2 "Por macroinstrução": O operador poderá solicitar a amostragem dos resultados ao fi nal da execução da sequência de microinstruções que interpreta uma dada macroinstrução.

- 3 "Por sequência de macroinstruções": Os dados serão listados na tela de acordo com o formato especificado pelo usuário, após a execução de um conjunto predefinido de macroins truções.

- Os "Modos de Leitura" que podem ser sele. cionados pelo usuário são:

- 1 Listar de uma só vez todo o conteúdo do REGISTRO DE ENTRADA da IAA em formato prede finido, que contém informações gerais do contexto do sistema microprogramado.

- 2 Informar o estado de um único bit do RE GISTRO DE ENTRADA.

- 3 Listar uma sequência de bits do REGISTRO DE ENTRADA, de tamanho variável especificado pelo usuário.

## 4. CONCLUSÃO

O S-MICRO encontra-se atualmente em fase de desenvolvimento, com o "hardware" totalmen te configurado e com o SS ja específicado nu ma primeira versão e programado na linguagem de alto nível, ALGOL-M.

A primeira aplicação deste sistema 'serã no desenvolvimento do Processador PISB (emu lação domicroprocessador SBP9900 da Texas Ins truments). O "software" que simula a unidade de controle deste processador foi especifica do e incorporado ao "Software de Simulação." O microprograma desta unidade está sendo de senvolvido com o auxílio da linguagem LMP e espera-se que esse sistema forneça meios su ficientes para a validação e especificação con conjuntas da arquitetura da unidade de trole, do microprograma e dos recursos de di "hardware" do Processador PISB. Pode-se zer que, sem o apoio de um sistema semelhan te, o grau de dificuldade para a validação do Processador PISB seria muito maior.

Com a experiência já adquirida no desen volvimento do S-MICRO, notou-se que um possí vel aperfeiçoamento do sistema proposto pode ria ocorrer com o desenvolvimento de uma linguagem que possibilitasse a definição, de forma flexível, da arquitetura da unidade de controle atraves da definição, específicação e integração de módulos funcionais basicos que compoem normalmente uma unidade de controle microprogramada.

Os sistemas de desenvolvimento para sis temas microprogramados existentes hoje comer cialmente (como o AmSYS<sup>TM</sup>29 da Advanced Micro Devices ou os equipamentos da Step Engineering) diferem em essencia do S-MICRO, uma vez que nestes sistemas a unidade de Con trole Microprogramada é emulada ao nível do "Hardware" quase em sua totalidade, enquanto que no S-MICRO toda a lógica de sequenciamen to é simulada ao nível do "Software" como ja foi dito.

Não temos informação alguma sobre simila res nacionais.

### 5. REFERÊNCIAS BIBLIOGRÁFICAS

- Amaral, P.F.S., (1979). Emulador de Memorias de Microcontrole Auxiliado por Computa dor, INFE, São Jose dos Campos. Tese de Mestrado em Eletronica e Telecomunica. ções. (INPE-1489-TDL/009).

- Yamaguti, W., (1981). LMP, Uma Linguagem de Microprogramação, INPE, São José dos Campos. Tese de Mestrado em Eletrônica e Telecomunicações. (INPE-2031-TLD/049).

- Martins, R.C.O., (1976). Algol-M Uma Linguagem de Alto Nivel para microcomputa dores, INPE, São José dos Campos. Tese de Mestrado em Computação Aplicada.